近日,集成电路设计顶会之一的IEEE定制集成电路大会(CICC 2024)在美国科罗拉多州丹佛举行,南方科技大学深港微电子学院有4篇论文入选。

深度神经网络模型部署在边缘设备上面临着模型越来越复杂、参数越来越大的挑战,为实现模型的高能效低成本的部署,该论文通过具有分层混合精度的NAS优化压缩模型大小,同时使用并行的矢量拆分与组合脉动阵列架构来高度利用硬件资源,实现混合精度网络的准确率等效到4位精度上,并实现等效于2位精度的高能效。该论文设计的芯片在28 nm CMOS工艺下完成测试,与国际最先进的研究工作,基于矢量的可拆分与组合实现的混合精度实现了最高的峰值能效(63.54 TOPS/W)和最高的峰值面积效率(7.94 TOPS/mm2)。在混合精度模型加速上,基于NAS优化的混合精度VGG-16模型实现了平均能效达29.12 TOPS/W(等效于2位精度的能效),同时准确率达70.148%(等效于4位精度的准确率)。该工作实现了最好的能效和面积效率以及实现了模型的低成本和高能效部署。

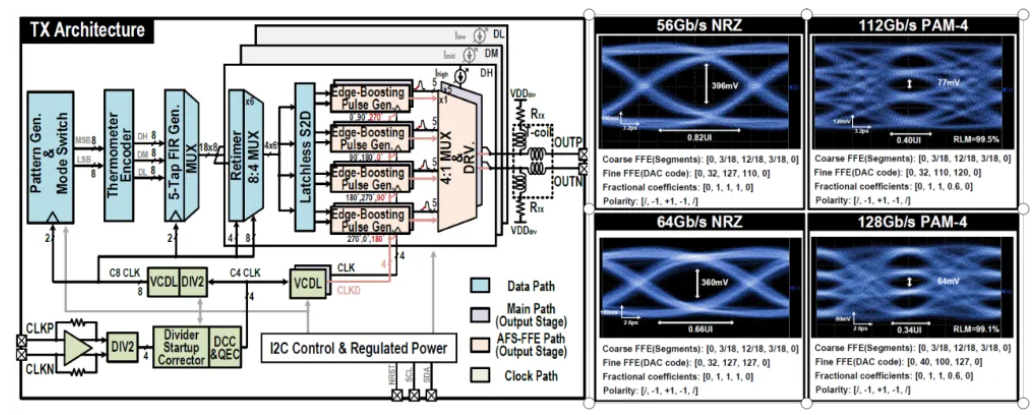

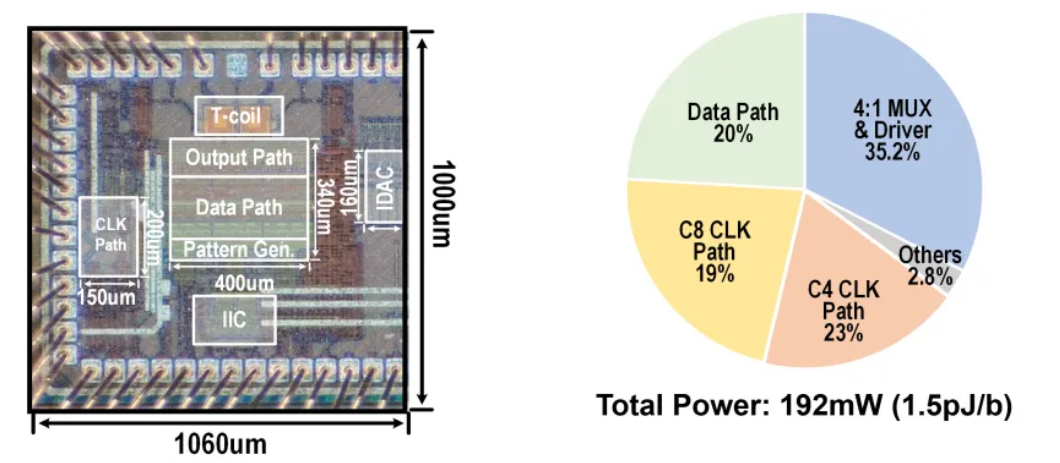

在云计算和人工智能应用中,需要高性能数据中心来处理和交换海量数据。这种不断增长的吞吐量需求推动了高数据速率的有线发射机的发展。近年来,有线Gb/s的数据速率。然而,由于PAM-4信令的中间眼睛和顶部/底部眼睛之间的边缘过渡时间不同,PAM-4信令的眼图表现出不等的转换沿抖动,导致水平眼睛张开度降低和信号完整性恶化。针对该问题,这项工作提出了一种128Gb/s四电平调制的有线发射机来减轻该信号完整性问题。所提出的预加重非对称分数间隔前馈均衡器处理了PAM-4眼图中的不等的转换沿抖动,并实现了水平眼宽开云网站的拓展。此外,还采用了额外的5抽头单位间隔前馈均衡器来提高均衡器的精度。在发射器输出驱动级中,提出的边缘提升脉冲发生器提高了带宽,从而加快了TX输出信号的边缘转换速度。在串化链路中,利用锁存最小化串行器来优化了数据路径的功耗和面积。

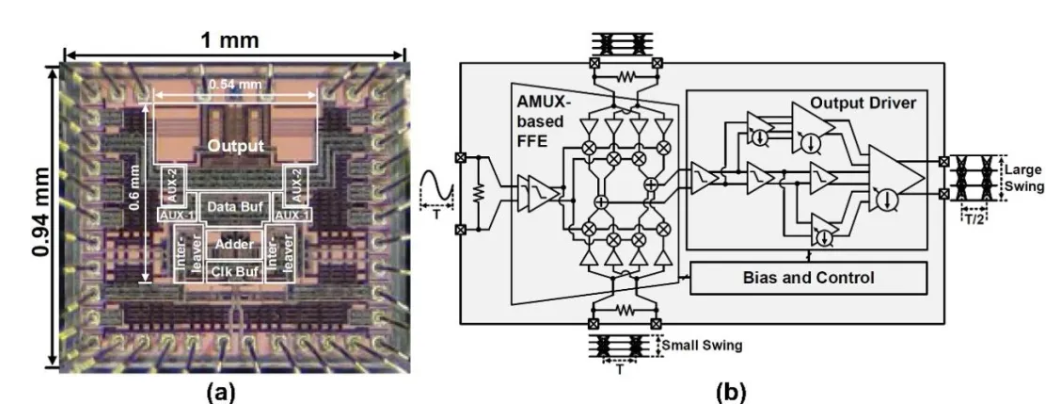

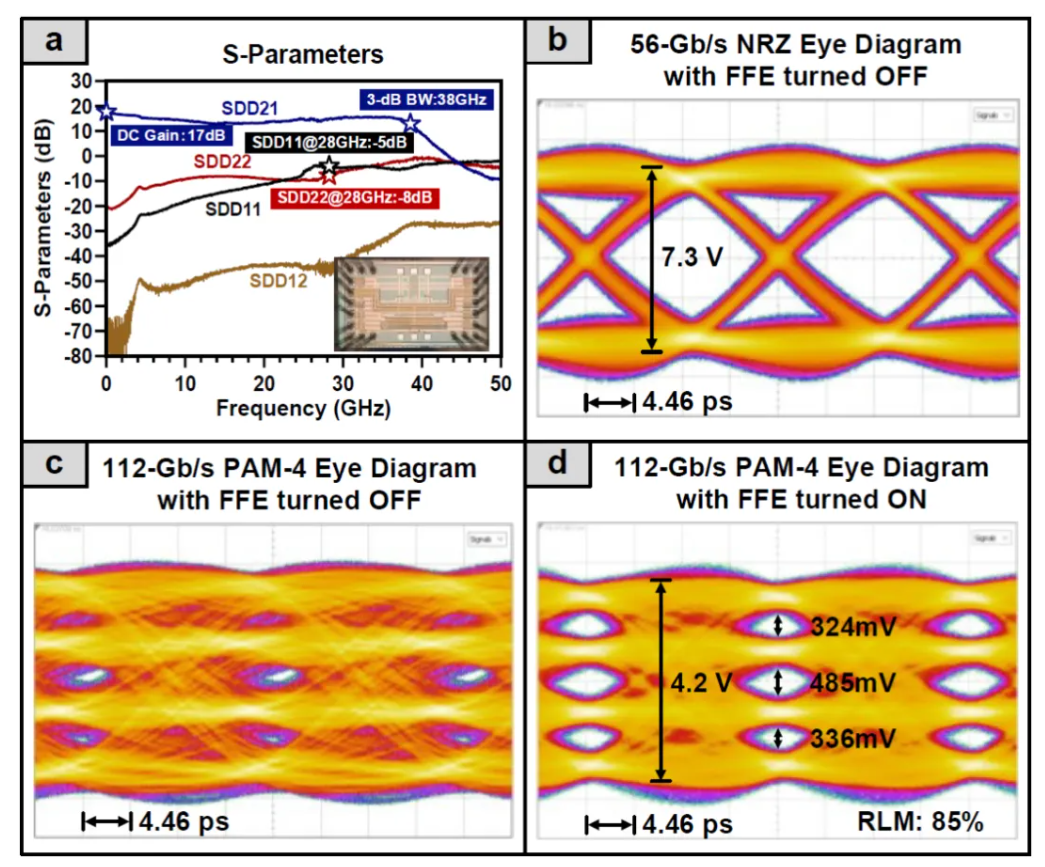

光调制器如Mach-Zehnder调制器(MZM)正在成为数据中心互连和长距离光通信中不可或缺的组件。为了产生高速高消光比(ER)的光信号,光调制器需要具有大输出摆幅的高带宽发射机。同时,发射机端也需要进行均衡,对电信号进行预失真,并补偿电光表面和光学器件的高频损耗。由于脉冲幅度调制信号(如PAM-4)具有高调制效率,发射机的线性度成为一个重要问题。近年来已经提出了用于光调制器的线性发射机。然而,由于线性度有限,它们在高数据速率操作Kaiyun官方中国下的输出摆幅较小。如基于InP技术的光调制器线性发射机,实现了模拟复用器(AMUX)以减轻数字模拟转换器(DAC)的带宽要求,但其小的输出摆幅和缺乏均衡限制了应用。在本工作中,提出了一种具有可重构前馈均衡(FFE)的大摆幅线性发射机。发射机主要由基于AMUX的FFE和输出驱动器组成。AMUX既作为2:1串行器,又作为均衡器。输出驱动器放大来自AMUX的预失真数据流,并将大摆幅信号传送给后续的光调制器。除了具备2:1串行化和可重构的FFE功能外,该发射机还实现了最高的数据速率-输出摆幅乘积,最低的驱动器总谐波失真(THD)和最佳的性能指标(FoM)。

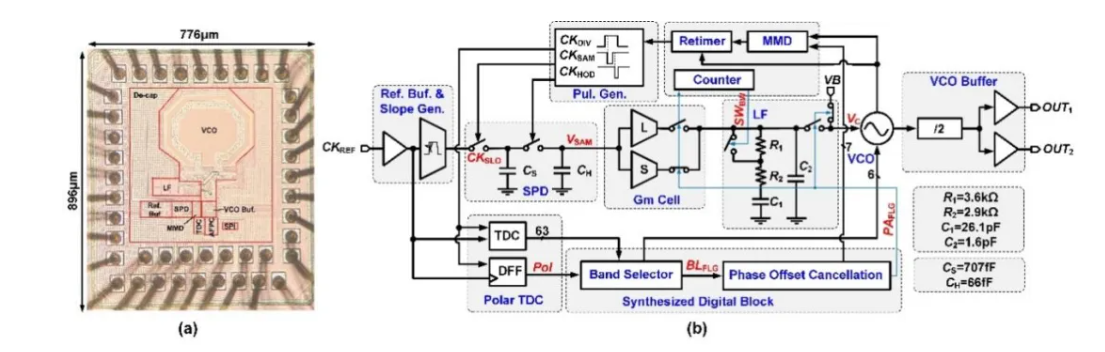

图7.PAM-4信令高线性度高摆幅发射机(a)芯片显微图和(b)系统架构图

图8.(a)发射机输出驱动器的S参数以及发射机的(b)-(d)眼图测试结果

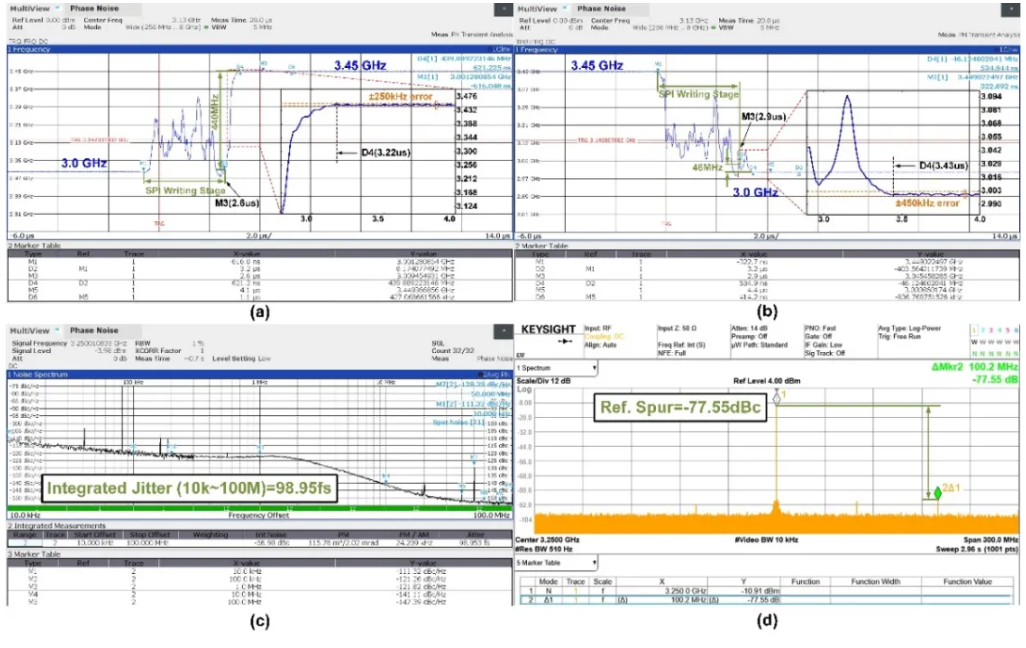

频率合成器的建立时间在决定现代无线和有线系统的动态性能方面起着至关重要的作用,这些系统采用功率门控和动态电压频率调节技术来降低功耗。全数字锁相环及其数字环路滤波器因其快速收敛速度和与数字算法的兼容性而成为模拟锁相环的卓越替代品。然而,这些方法需要具有灵活可编程性的数字环路滤波器。因此,为数字锁相环开发的快速锁定技术不能直接缓解到低抖动II型采样锁相环,使用高增益但窄捕获范围的采样鉴相器和有限的可编程模拟环路滤波器。本文提出了一种6.0至6.9GHz采样锁相环,通过所提出的自动频率和相位校准(AFPC)方法实现99fsrms抖动和0.62μs(62TREF)的锁定时间。为了解决锁定时间和功耗的挑战,论文提出了一种基于64位时间数字转换器(TDC)的AFPC方法,该方法可以有效地加速频率和相位锁定阶段。在锁频过程中,降低频带选Kaiyun官方中国择的时间,即搜索开关电容控制字的时间,从传统二进制搜索算法中的几微秒缩短到不到半微秒。此外,剩余的锁相阶段受益于TDC在相位偏移消除(POC)阶段对清晰初始状态的贡献,从而以最小的硬件成本实现更快的锁定。通过精心设计的捕获范围,防止在频率相位锁定后出现“捕获出窗”导致的长锁定时间。该方法具有快速收敛、架构简单、TDC分辨率要求宽松和鲁棒性高的特点。

图9.快速频率相位锁定II型采样锁相环(a)芯片显微图和(b)系统架构图

图10.(a)6.0-6.9GHz锁定测试结果,(b)6.9-6.0GHz锁定测试结果,(c)6.5GHz输出抖动测试结果,(d)6.5GHz输出参考杂散抑制测试结果

CICC是IEEE固态电路协会(Solid-State Circuits Society)主办的定制集成电路会议(CICC)是集成电路设计领域顶级会议之一,以论文录用率低、作品创新性和实用性强著称,每年吸引全球范围内大量学术界、工业界研发人员的关注和参与。会议内容涉及模拟电路设计、生物医学、传感器、显示器和MEMS,数字和混合信号SoC/ASIC/SIP,嵌入式存储器件等方面,重点讨论如何解决集成电路设计问题的方法,以提高芯片各项性能指标。

中国科学院上海技术物理研究所位相调控光电耦合奇异点增强的磁子频率梳研究获进展

赛迪半导体完成数千万元A+轮融资,聚焦笔电PD & USB4 ReTimer芯片开发

Copyright © 2024 开云沙盘有限公司 版权所有 备案号:蜀ICP备19012180号 网站地图